Product Summary

The IP1001 is a fully optimized solution for high current synchronous buck applications requiring up to 20A. The IP1001 is optimized for single-phase applications, and includes a full function fast transient response PWM control, with an optimized power semiconductor chip-set and associated passives, achieving benchmark power density. Very few external components are required, including output inductor, input & output capacitors. Further range of operation to 3.3Vin can be achieved with the addition of a simple external boost circuit, and operation up to 3.3Vout can be achieved with a simple external voltage divider.

Parametrics

IP1001 absolute maximum ratings: (1)VIN to PGND: -0.3 to 16.0 v; (2)VDD to PGND: -0.3 to 6.0v; (3)VFS: -0.3 to VDD+0.3 v; (4)VF: -0.3 to VDD+0.3; (5)D0-D4: -0.3 to VDD+0.3; (6)PGOOD to PGND: -0.3 to 6.0; (7)ENABLE to PGND: -0.3 to 6.0; (8)ILIM: -0.3 to VDD+0.3; (9)FREQ: -0.3 to VDD+0.3; (10)Output RMS Current: 20 A max; (11)Block Temperature, TBLK: -40 to 125 ℃.

Features

IP1001 features: (1)3.3V to 12V input voltage; (2)20A maximum load capability, with no derating up to TPCB = 90℃; (3)5 bit DAC settable, 0.925V to 2V output voltage range; (4)Configurable down to 3.3Vin & up to 3.3Vout with simple external circuit; (5)200kHz or 300kHz nominal switching frequency; (6)Optimized for very low power losses; (7)Over & undervoltage protection; (8)Adjustable lossless current limit; (9)Internal features minimize layout sensitivity; (10)Very small outline 14mm x 14mm x 3mm.

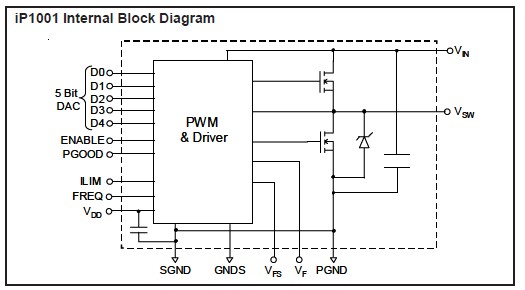

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

IP1001 |

|

IC REG BUCK SYNC ADJ 20A 256BGA |

Data Sheet |

Negotiable |

|

|||||

|

IP1001LF |

Other |

|

Data Sheet |

Negotiable |

|

||||

IP1001TR |

|

IC REG BUCK SYNC ADJ 20A 256BGA |

Data Sheet |

Negotiable |

|

|||||

(China (Mainland))

(China (Mainland))